Attached files

| file | filename |

|---|---|

| 8-K - MOSYS, INC. 8-K - MoSys, Inc. | a6163828.htm |

| EX-99.1 - EXHIBIT 99.1 - MoSys, Inc. | a6163828ex99_1.htm |

Exhibit 99.2

Announcing the NEW MoSys and Breakthrough Bandwidth Engine™ IC Product Family February 2, 2010 Dave DeMaria VP Business Operations, MoSys

Forward Looking Statements Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved. This presentation may contain forward-looking statements about MoSys, including, without limitation, expected benefits of the Bandwidth Engine ICs, product development and timing of shipments of Bandwidth Engine ICs, the capabilities and adoption of the GigaChip Interface, expected benefits and performance results expected from the use of MoSys’ embedded memory technologies and ICs, market size, growth of MoSys’ business and its future markets and future business prospects. Forward-looking statements are based on certain assumptions and expectations of future events that are subject to risks and uncertainties. Such statements are made in reliance upon the safe harbor provisions of Section 27A of the Securities Act of 1933 and Section 21E of the Securities Exchange Act of 1934. Actual results and trends may differ materially from historical results or those projected in any such forward-looking statements depending on a variety of factors. These factors include, but are not limited to: customer acceptance of the Bandwidth Engine IC; difficulties and delays in the development, production, testing and marketing of the Bandwidth Engine ICs; the anticipated costs and technological risks of developing and bringing ICs to market; the willingness of our manufacturing partners to assist successfully with the fabrication of Bandwidth Engine ICs; the availability of quantities of ICs supplied by our manufacturing partners at a competitive cost; our ability to generate the desired gross margin percentages and return on our product development investment; competition for our Bandwidth Engine ICs from established IC suppliers; the adequacy of our intellectual property protection for our proprietary IC designs and technologies; the vigor and growth of markets served by licensees, customers and prospects and of the operations of MoSys; our lack of recent experience as a fabless semiconductor company making and selling proprietary ICs; and other risks identified in MoSys’ most recent reports on forms 10-Q and 10-K filed with the Securities and Exchange Commission, as well as other reports that MoSys files from time to time with the Securities and Exchange Commission. MoSys undertakes no obligation to update publicly any forward-looking statement for any reason, except as required by law, even as new information becomes available or other events occur in the future.

February 2, 2010 ©MoSys, Inc. 2010. All Rights Reserved. Expanding MoSys Business Model from ‘IP licensing’ to ‘Fabless Semiconductor and IP’ Bandwidth EngineTM – Revolutionary Family of Serial ICs that Enable Breakthrough Performance in Networking Systems GigaChipTM Interface - Open Serial Interface to Enable EFFICIENT, High Speed Chip-to-Chip Communications MoSys is Announcing…

The New MoSys Vision Len Perham CEO, MoSys

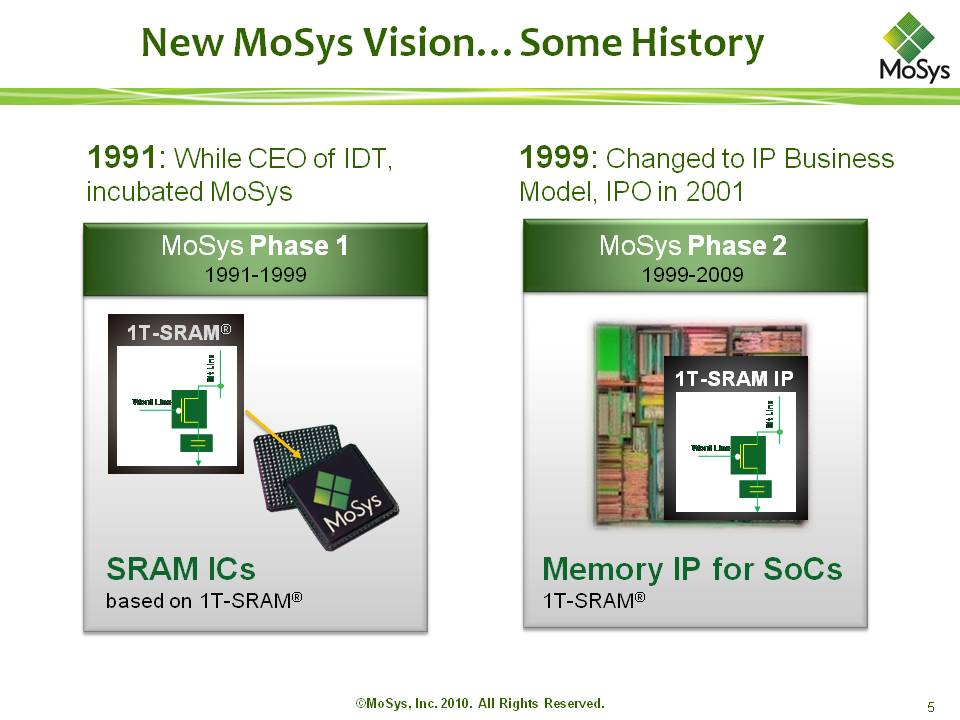

New MoSys Vision…Some History Body: 1991: While CEO of IDT, incubated MoSys SRAM ICs based on 1T-SRAM® 1T-SRAM® 1999: Changed to IP Business Model, IPO in 2001 MoSys Phase 1 1991-1999 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved. (Gp:) Memory IP for SoCs 1T-SRAM® (Gp:) MoSys Phase 2 1999-2009 (Gp:) 1T-SRAM IP

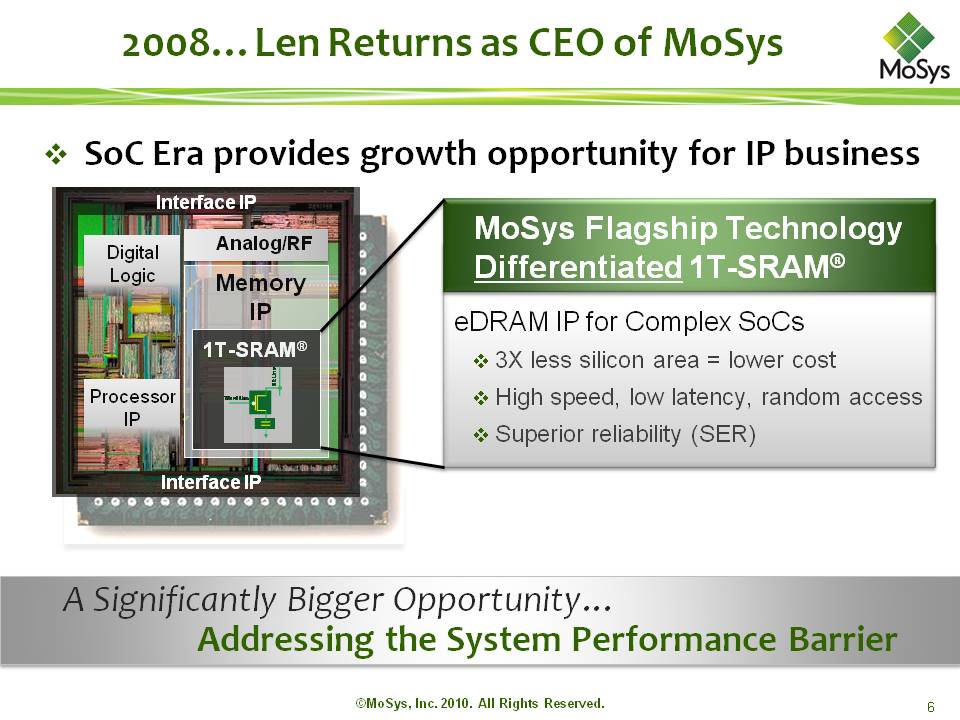

2008…Len Returns as CEO of MoSys eDRAM IP for Complex SoCs 3X less silicon area = lower cost High speed, low latency, random access Superior reliability (SER) Analog/RF Processor IP Memory IP 1T-SRAM® Interface IP Interface IP SoC Era provides growth opportunity for IP business MoSys Flagship Technology Differentiated 1T-SRAM® Digital Logic A Significantly Bigger Opportunity…Addressing the System Performance Barrier Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

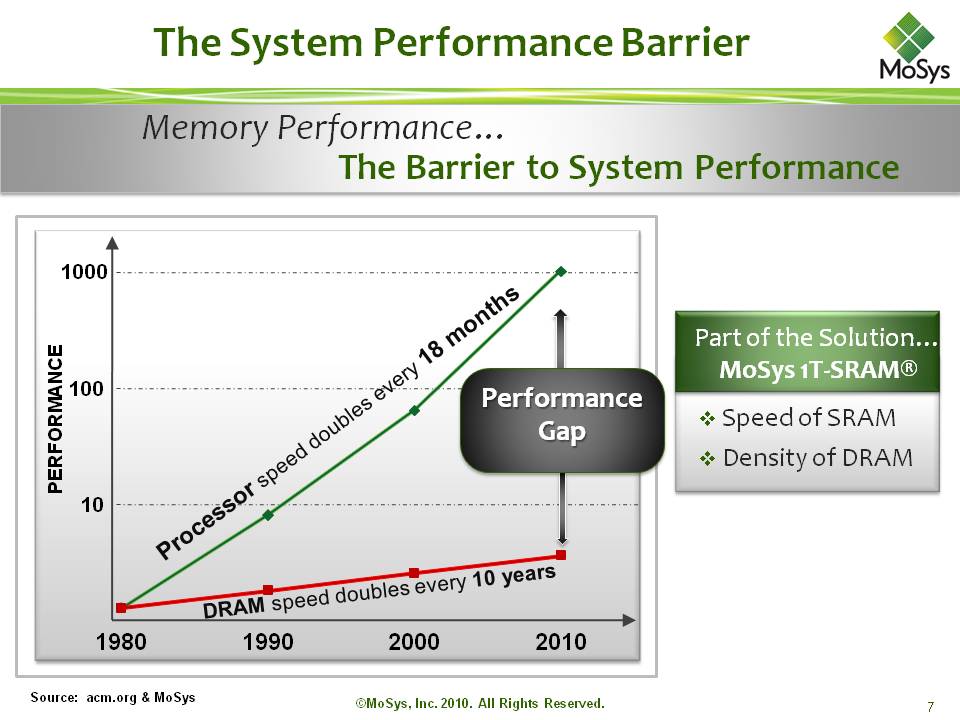

The System Performance Barrier Memory Performance…The Barrier to System Performance Source: acm.org & MoSys (Gp:) 10 (Gp:) 100 (Gp:) 1000 (Gp:) 1980 (Gp:) 1990 (Gp:) 2000 (Gp:) 2010 (Gp:) DRAM speed doubles every 10 years (Gp:) PERFORMANCE (Gp:) Processor speed doubles every 18 months (Gp:) Performance Gap (Gp:) Speed of SRAM Density of DRAM (Gp:) Part of the Solution…MoSys 1T-SRAM® Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

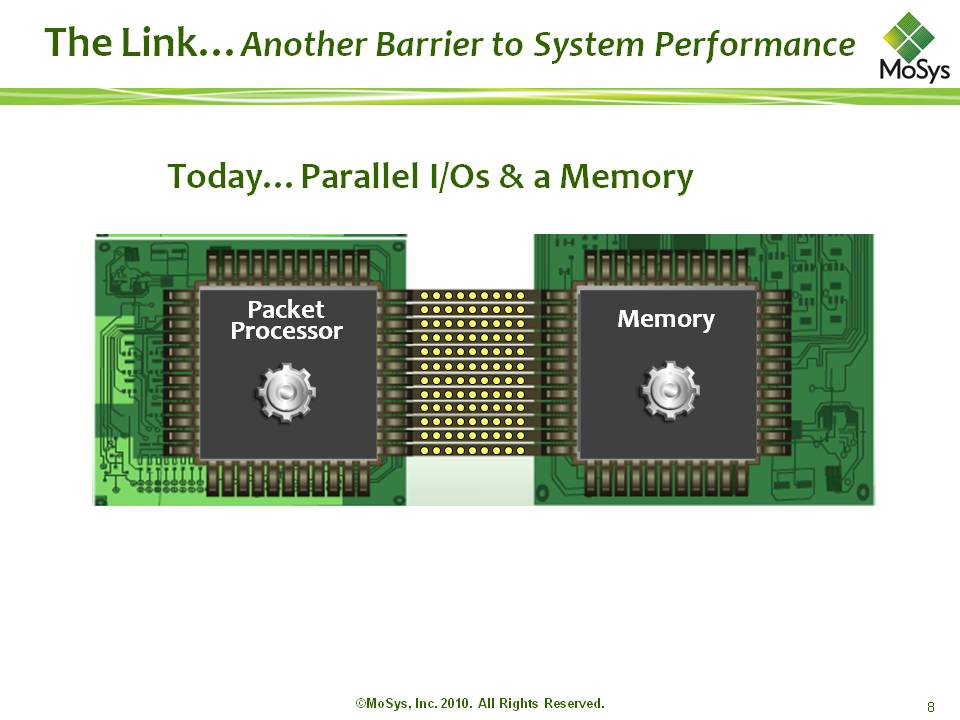

The Link…Another Barrier to System Performance Today…Parallel I/Os & a Memory Memory Packet Processor Memory Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

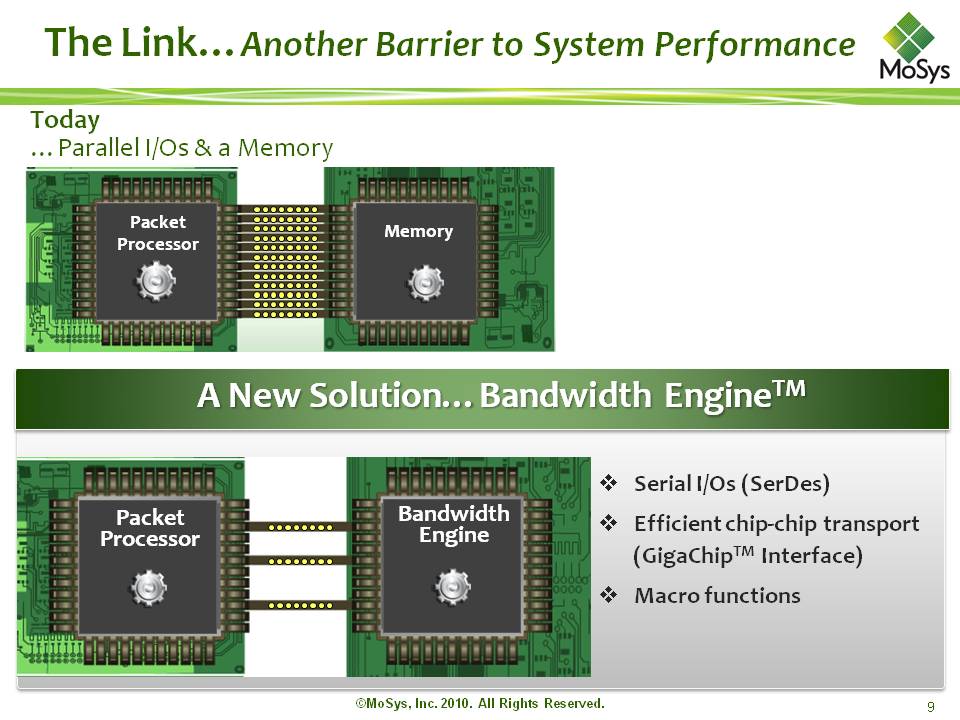

The Link…Another Barrier to System Performance Today…Parallel I/Os & a Memory Memory A New Solution…Bandwidth EngineTM Serial I/Os (SerDes) Efficient chip-chip transport (GigaChipTM Interface) Macro functions Memory Packet Processor Memory Bandwidth Engine Packet Processor Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

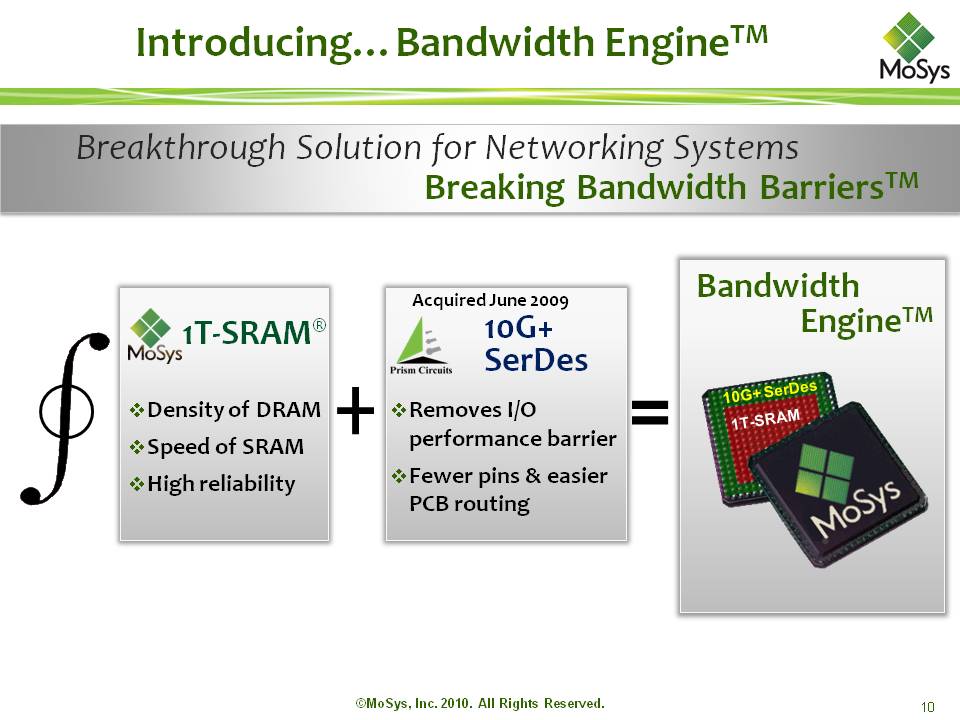

Introducing…Bandwidth EngineTM 1T-SRAM® Bandwidth EngineTM Density of DRAM Speed of SRAM High reliability10G+ SerDes Acquired June 2009 Removes I/O performance barrier Fewer pins & easier PCB routing Breakthrough Solution for Networking Systems Breaking Bandwidth BarriersTM Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

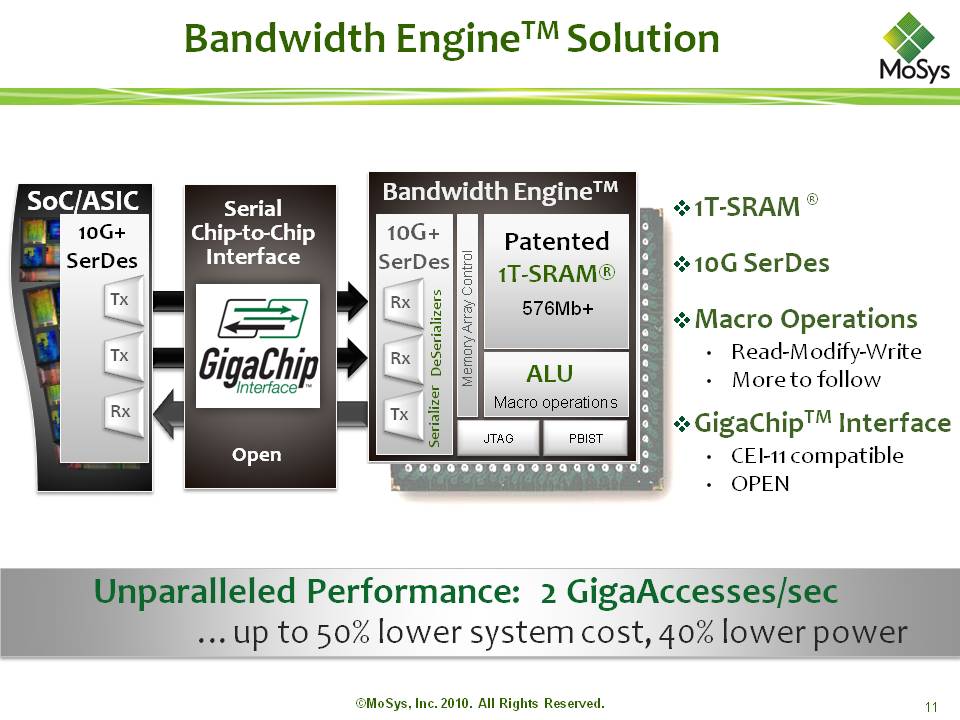

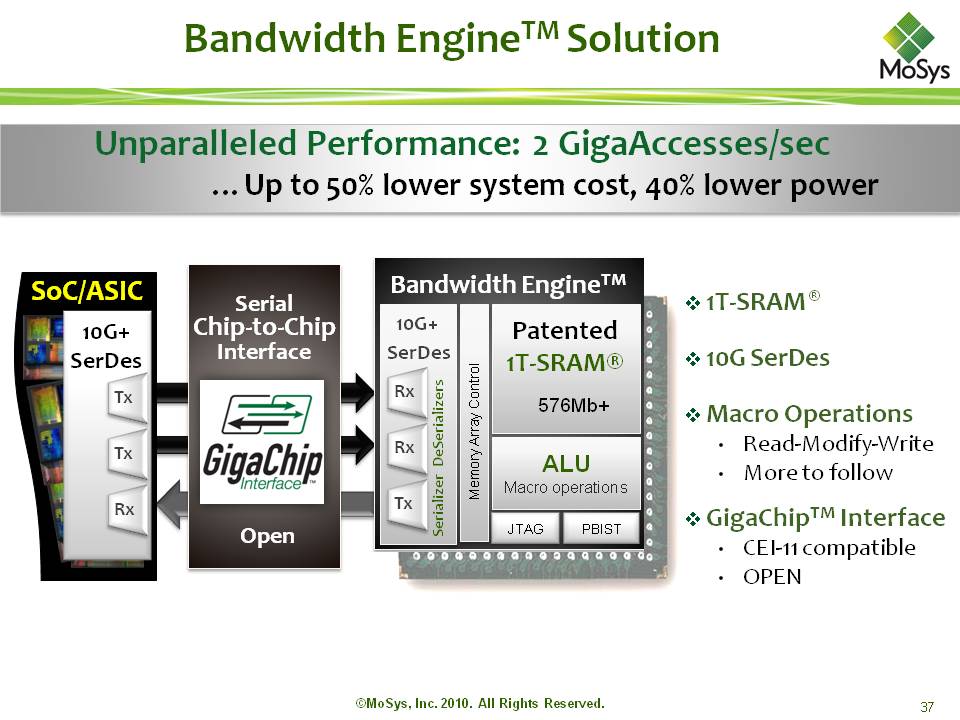

Bandwidth EngineTM Solution Patented 1T-SRAM® Memory Array Control 576Mb+ JTAG 10G+ SerDes DeSerializers Serializer Rx Rx Tx SoC/ASIC Tx Tx Rx 10G+ SerDes Bandwidth EngineTM PBIST ALU Macro operations GigaChipTM Interface CEI-11 compatible OPEN 10G SerDes Macro Operations Read-Modify-Write More to follow 1T-SRAM ® Unparalleled Performance: 2 GigaAccesses/sec…up to 50% lower system cost, 40% lower power Serial Chip-to-Chip Interface Open Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

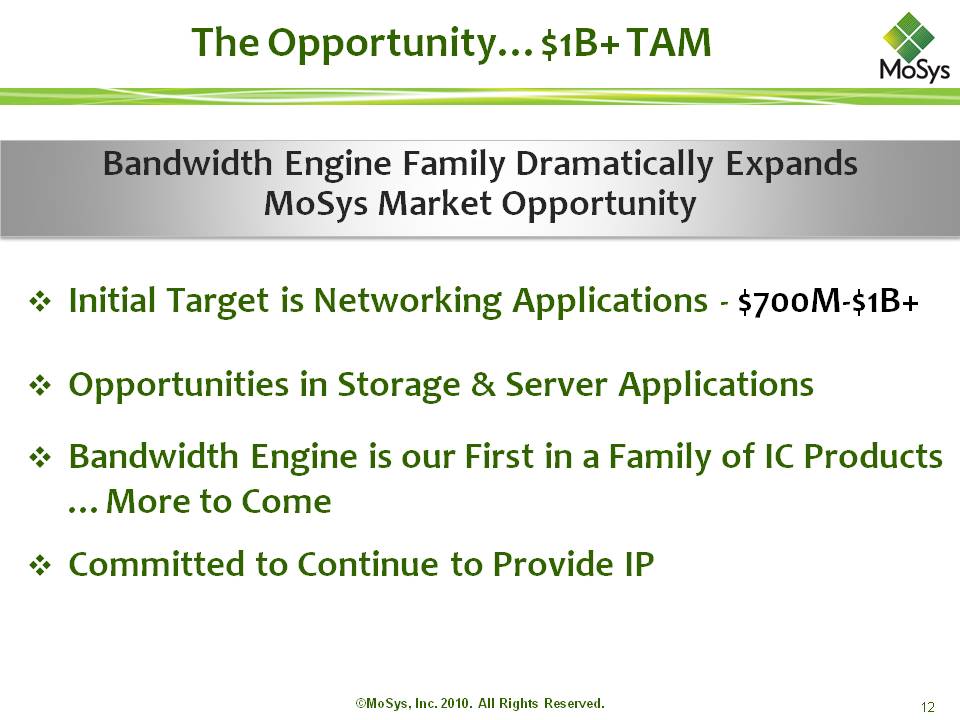

The Opportunity…$1B+ TAM Initial Target is Networking Applications - $700M-$1B+ Opportunities in Storage & Server Applications Bandwidth Engine is our First in a Family of IC Products…More to Come Committed to Continue to Provide IP Bandwidth Engine Family Dramatically Expands MoSys Market Opportunity Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

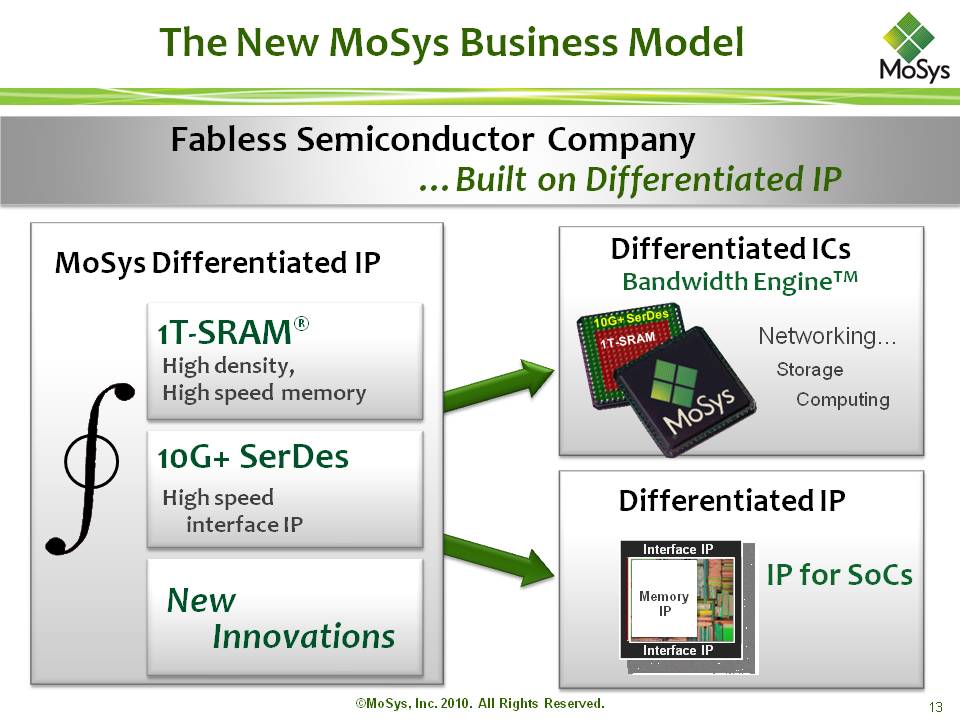

The New MoSys Business Model Differentiated ICs Networking…Storage Computing IP for SoCs Bandwidth EngineTM MoSys Differentiated IP 1T-SRAM® High density, High speed memory 10G+ SerDes High speed interface IP Differentiated IP New Innovations Fabless Semiconductor Company…Built on Differentiated IP (Gp:) Memory (Gp:) IP (Gp:) Interface IP (Gp:) Interface IP Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved

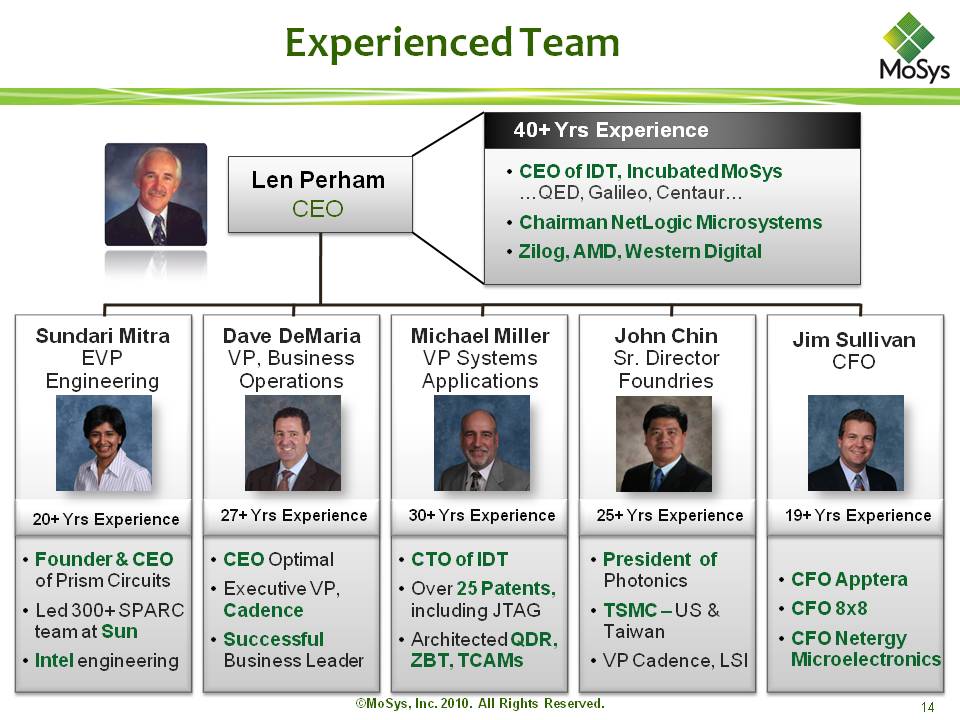

Experienced Team Len Perham CEO Founder & CEO of Prism Circuits Led 300+ SPARC team at Sun Intel engineering Dave DeMaria VP, Business Operations John Chin Sr. Director Foundries Sundari Mitra EVP Engineering Jim Sullivan CFO Michael Miller VP Systems Applications 20+ Yrs Experience CEO Optimal Executive VP, Cadence Successful Business Leader 27+ Yrs Experience CTO of IDT Over 25 Patents, including JTAG Architected QDR, ZBT, TCAMs 30+ Yrs Experience President of Photonics TSMC – US & Taiwan VP Cadence, LSI 25+ Yrs Experience CFO Apptera CFO 8x8 CFO Netergy Microelectronics 19+ Yrs Experience 40+ Yrs Experience CEO of IDT, Incubated MoSys…QED, Galileo, Centaur…Chairman NetLogic Microsystems Zilog, AMD, Western Digital Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

Bandwidth Engine™ Breaking Bandwidth Barriers Michael Miller VP, Technology Innovation & System Applications

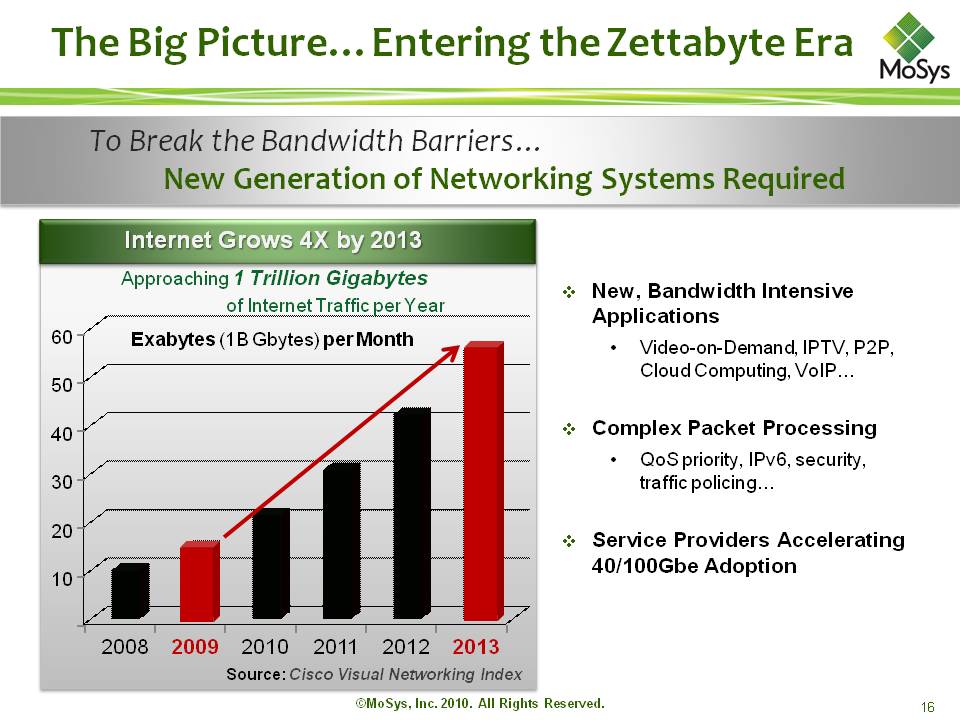

The Big Picture…Entering the Zettabyte Era Body: Internet Grows 4X by 2013 Exabytes (1B Gbytes) per Month Source: Cisco Visual Networking Index New, Bandwidth Intensive Applications Video-on-Demand, IPTV, P2P, Cloud Computing, VoIP…Complex Packet Processing QoS priority, IPv6, security, traffic policing… Service Providers Accelerating 40/100Gbe Adoption 10 20 30 40 50 60 2008 2009 2010 2011 2012 2013 Approaching 1 Trillion Gigabytes of Internet Traffic per Year To Break the Bandwidth Barriers…New Generation of Networking Systems Required Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

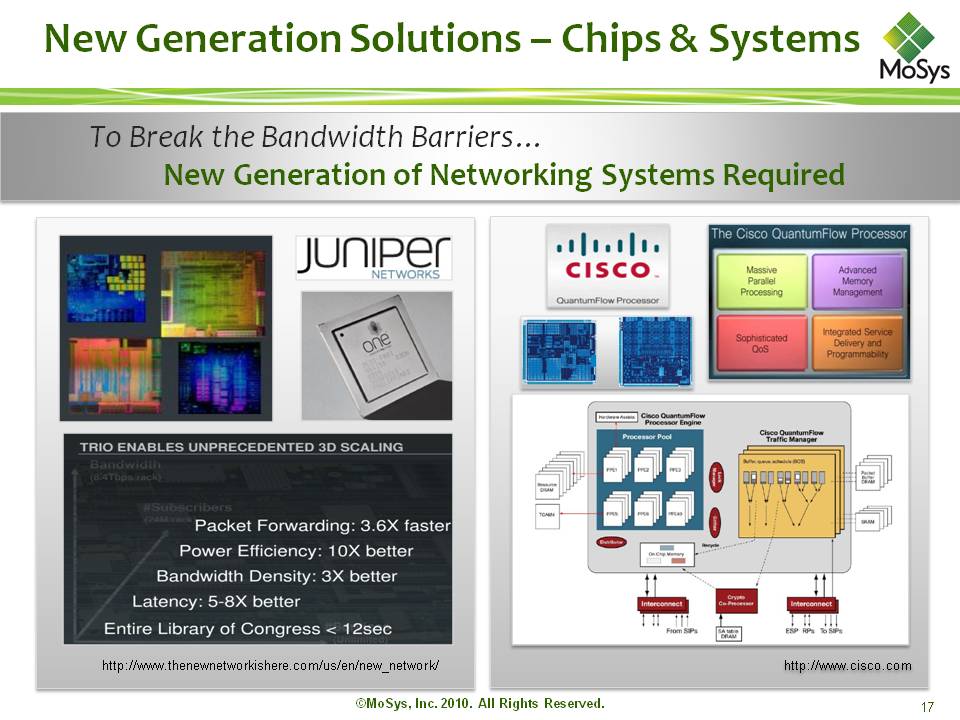

New Generation Solutions – Chips & Systems http://www.thenewnetworkishere.com/us/en/new_network/ (Gp:) http://www.cisco.com To Break the Bandwidth Barriers…New Generation of Networking Systems Required Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

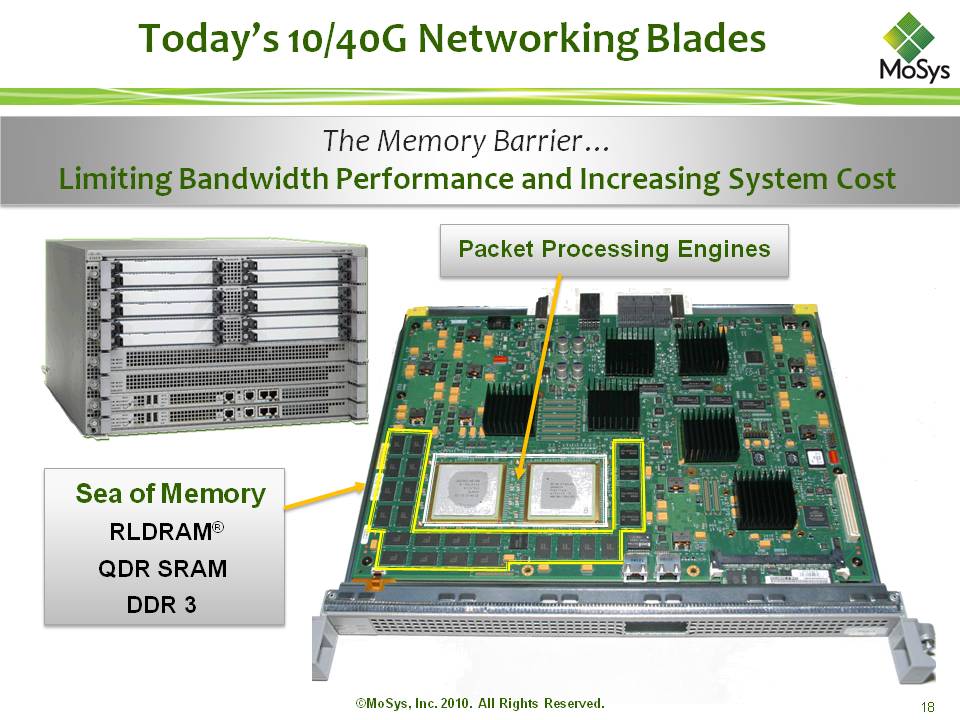

Today’s 10/40G Networking Blades RLDRAM® QDR SRAM Packet Processing Engines Sea of Memory The Memory Barrier… Limiting Bandwidth Performance and Increasing System Cost DDR 3 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

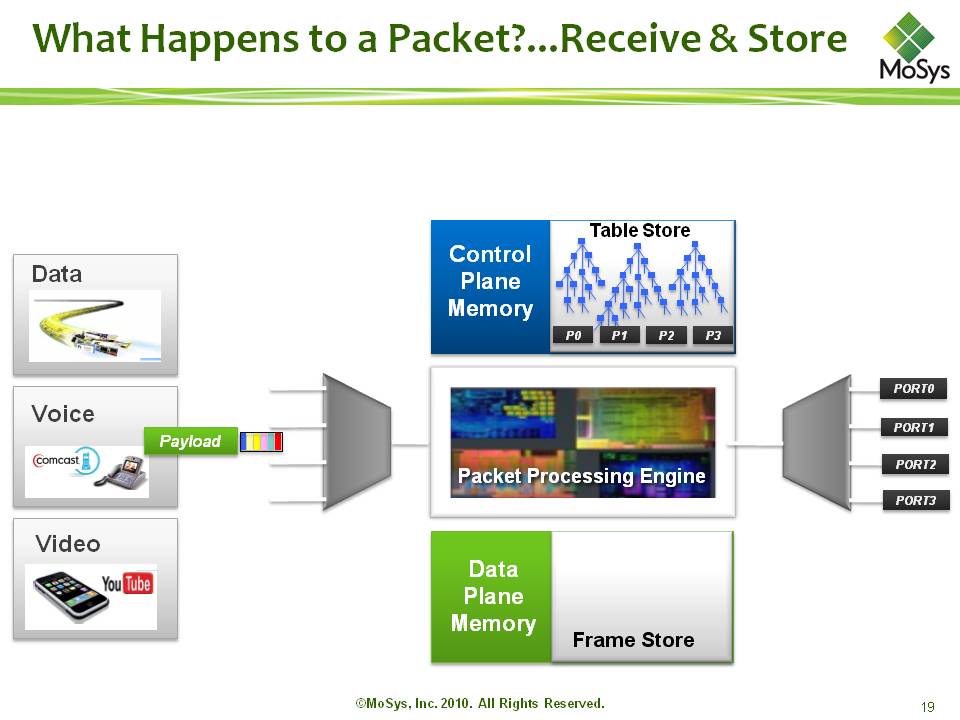

Data Plane Memory Packet Processing Engine PORT0 PORT1 PORT2 PORT3 Frame Store Table Store Control Plane Memory 19 Title: What Happens to a Packet?...Receive & Store Video Data Voice Payload Frame Store P0 P1 P2 P3 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

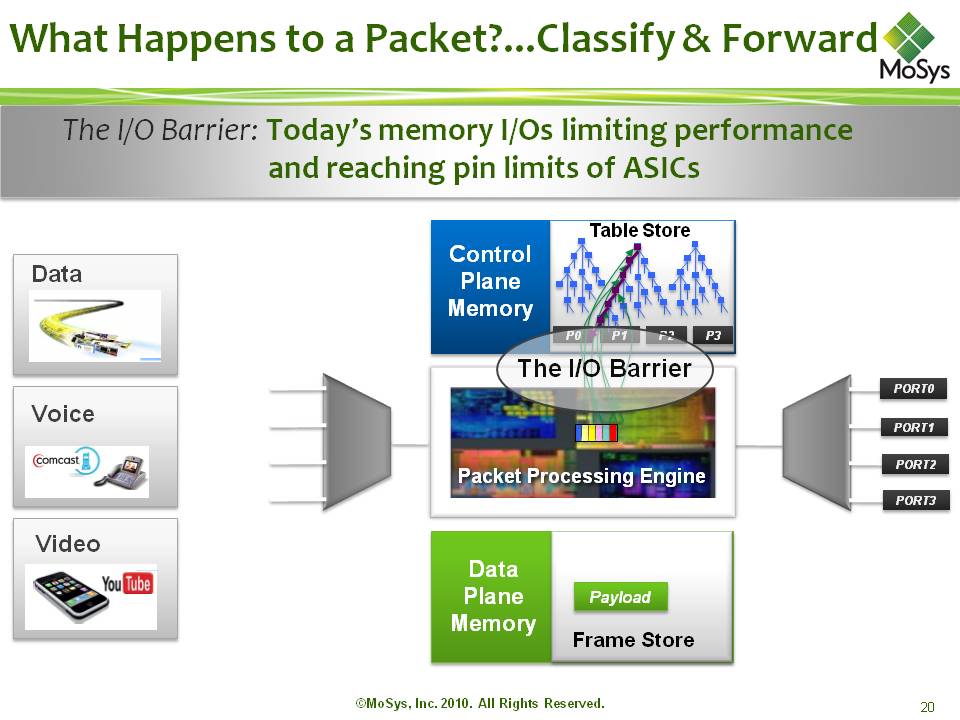

(Gp:) P0 (Gp:) P1 (Gp:) P2 (Gp:) P3 Packet Processing Engine PORT0 PORT1 PORT2 PORT3 20 Title: What Happens to a Packet?...Classify & Forward Payload Frame Store Table Store Control Plane Memory Data Plane Memory The I/O Barrier: Today’s memory I/Os limiting performance and reaching pin limits of ASICs Video Data Voice (Gp:) The I/O Barrier Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

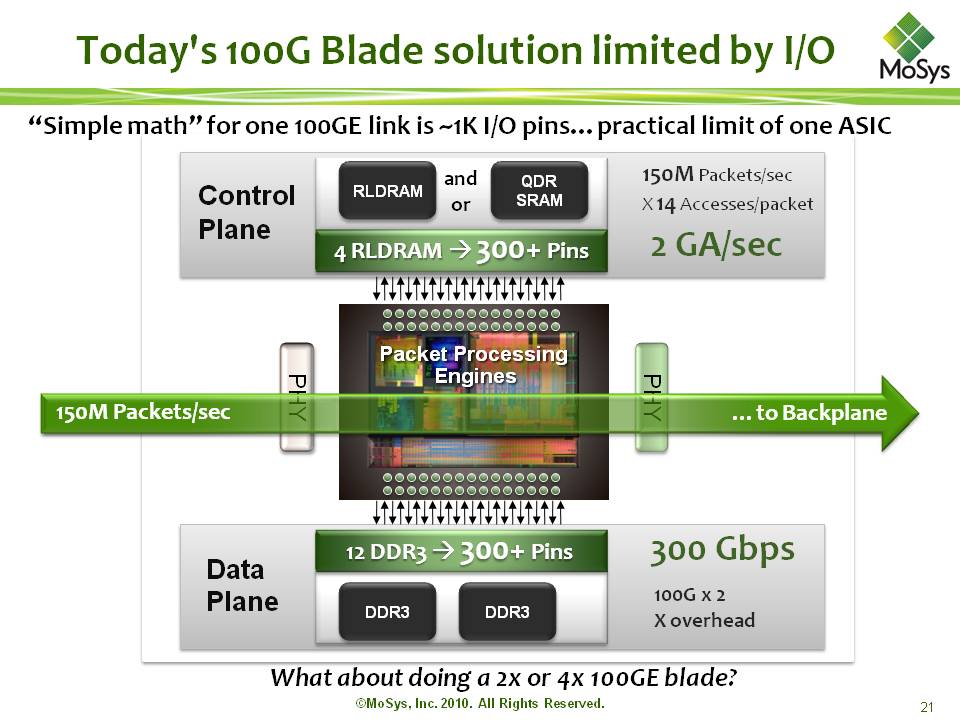

Packet Processing Engines Title: Today's 100G Blade solution limited by I/O Other Placeholder: 21 PHY PHY “Simple math” for one 100GE link is ~1K I/O pins…practical limit of one ASIC What about doing a 2x or 4x 100GE blade? Control Plane RLDRAM QDR SRAM and or 150M Packets/sec X 14 Accesses/packet 2 GA/sec (Gp:) 150M Packets/sec (Gp:) …to Backplane Data Plane DDR3 DDR3 100G x 2 X overhead 300 Gbps (Gp:) 4 RLDRAM ? 300+ Pins (Gp:) 12 DDR3 ? 300+ Pins Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

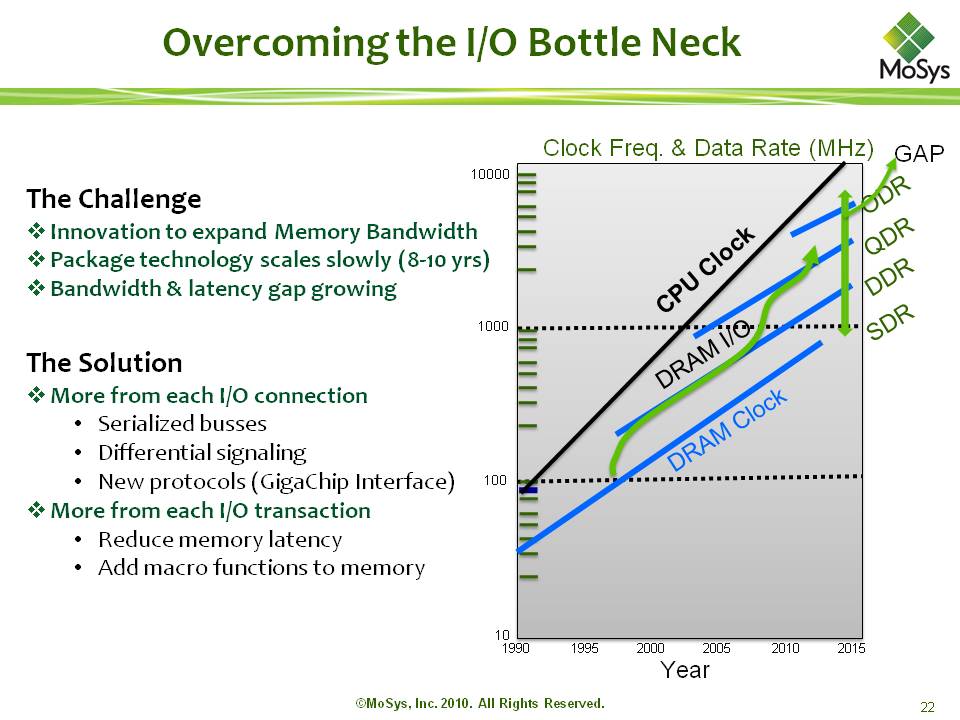

Overcoming the I/O Bottle Neck (Gp:) 1990 1995 2000 2005 2010 2015 (Gp:) 10000 (Gp:) Year (Gp:) SDR (Gp:) ODR (Gp:) QDR (Gp:) DDR (Gp:) 10 (Gp:) CPU Clock (Gp:) DRAM Clock (Gp:) DRAM I/O (Gp:) Clock Freq. & Data Rate (MHz) (Gp:) 1000 (Gp:) 100 (Gp:) GAP The Challenge Innovation to expand Memory Bandwidth Package technology scales slowly (8-10 yrs) Bandwidth & latency gap growing The Solution More from each I/O connection Serialized busses Differential signaling New protocols (GigaChip Interface) More from each I/O transaction Reduce memory latency Add macro functions to memory Other Placeholder: 22 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

Introducing the Bandwidth EngineTM Bandwidth: rate at which information is transferred over a communication channel Engine: mechanism to power or automate a task at a high rate Rate Data Packets, frames or sectors can be stored & forwarded Rate Control Information can be accessed to steer packets, frames or sectors MoSys Bandwidth EngineTM A Bandwidth Breakthrough for Networking Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

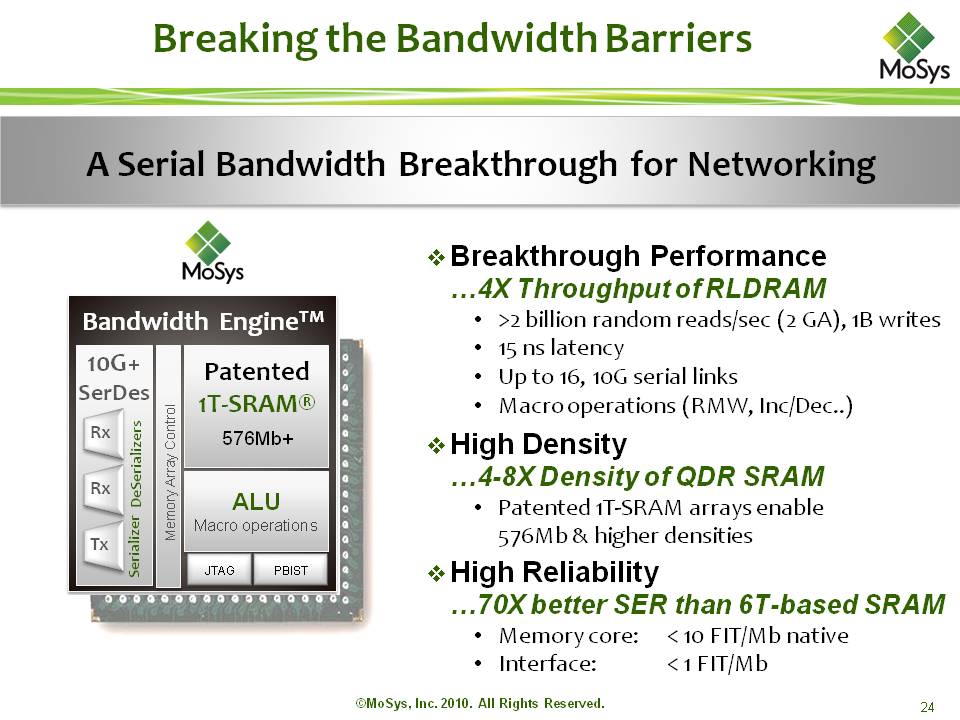

Breaking the Bandwidth Barriers Breakthrough Performance…4X Throughput of RLDRAM >2 billion random reads/sec (2 GA), 1B writes 15 ns latency Up to 16, 10G serial links Macro operations (RMW, Inc/Dec..) High Density …4-8X Density of QDR SRAM Patented 1T-SRAM arrays enable 576Mb & higher densities High Reliability…70X better SER than 6T-based SRAM Memory core: < 10 FIT/Mb native Interface: < 1 FIT/Mb Patented 1T-SRAM® Memory Array Control 576Mb+ JTAG 10G+ SerDes DeSerializers Serializer Rx Rx Tx PBIST ALU Macro operations Bandwidth EngineTM A Serial Bandwidth Breakthrough for Networking Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

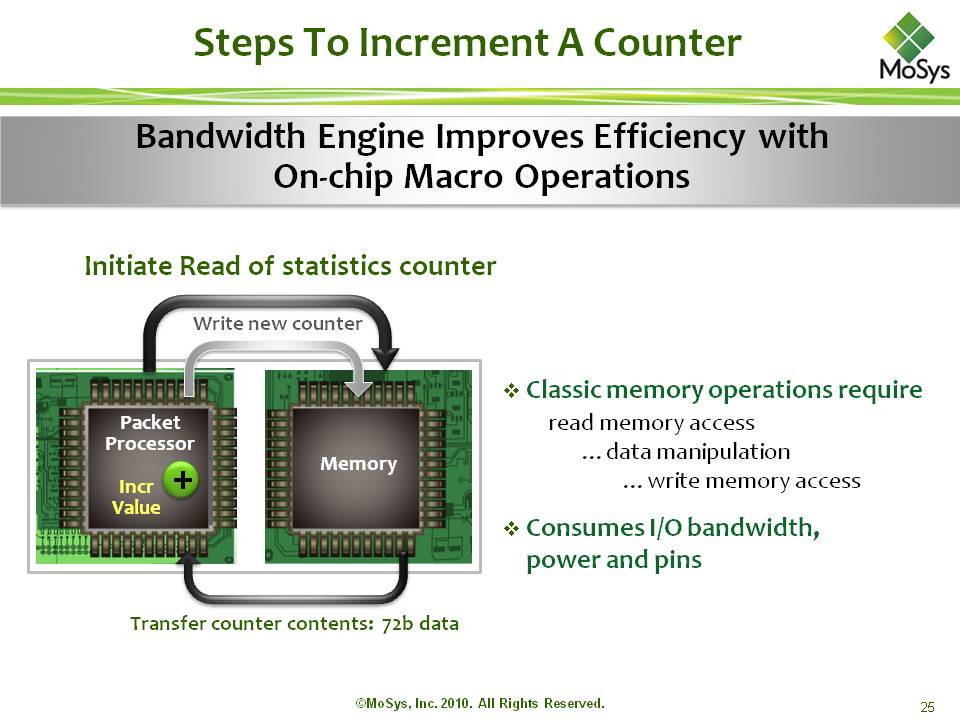

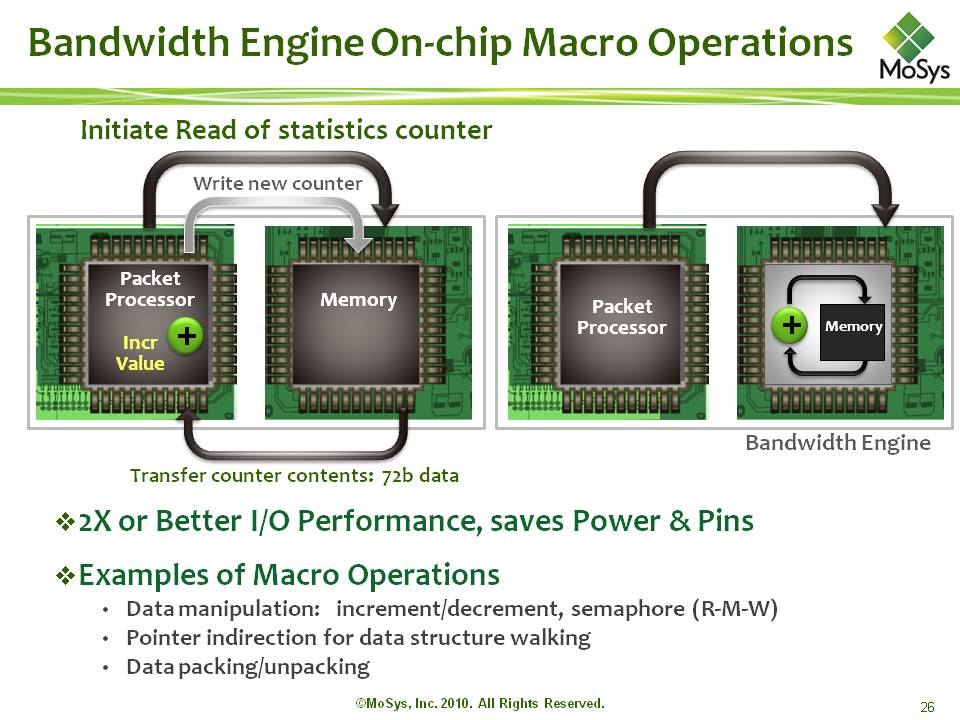

Steps To Increment A Counter Memory Packet Processor Transfer counter contents: 72b data Initiate Read of statistics counter (Gp:) + (Gp:) Incr Value Write new counter Classic memory operations require read memory access…data manipulation…write memory access Consumes I/O bandwidth, power and pins Bandwidth Engine Improves Efficiency with On-chip Macro Operations Other Placeholder: 25 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

(Gp:) Bandwidth Engine (Gp:) Packet Processor Title: Bandwidth Engine On-chip Macro Operations Memory Packet Processor Transfer counter contents: 72b data Initiate Read of statistics counter (Gp:) + (Gp:) Incr Value Write new counter (Gp:) + (Gp:) Memory 2X or Better I/O Performance, saves Power & Pins Examples of Macro Operations Data manipulation: increment/decrement, semaphore (R-M-W) Pointer indirection for data structure walking Data packing/unpacking Other Placeholder: 26 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

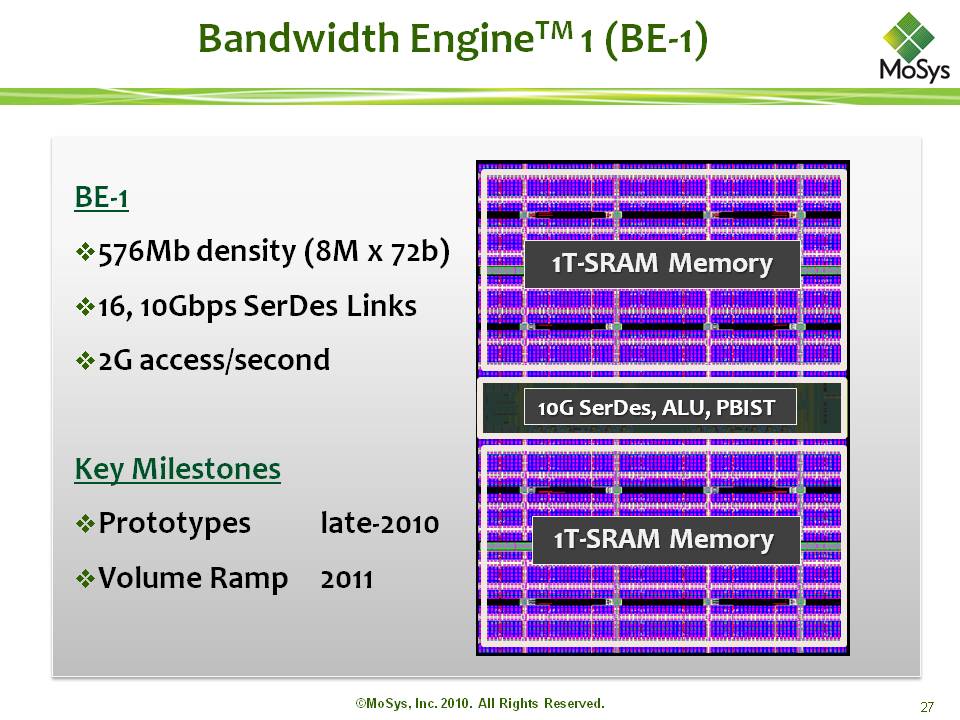

Bandwidth EngineTM 1 (BE-1) BE-1 576Mb density (8M x 72b) 16, 10Gbps SerDes Links 2G access/second Key Milestones Prototypes late-2010 Volume Ramp 2011 1T-SRAM Memory 10G SerDes, ALU, PBIST 1T-SRAM Memory Other Placeholder: 27 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

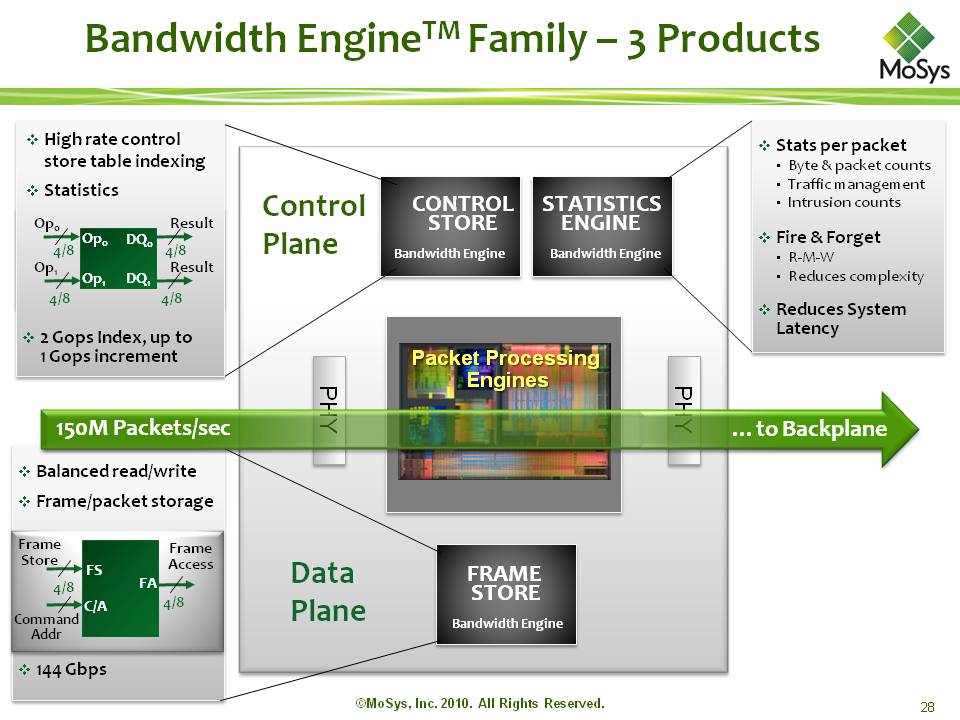

Bandwidth EngineTM Family – 3 Products Packet Processing Engines PHY PHY Control Plane Data Plane Bandwidth Engine CONTROL STORE Bandwidth Engine STATISTICS ENGINE Bandwidth Engine FRAME STORE (Gp:) Op1 (Gp:) DQ0 (Gp:) DQ1 (Gp:) Op0 (Gp:) Op1 (Gp:) 4/8 (Gp:) Op0 (Gp:) 4/8 (Gp:) Result (Gp:) Result (Gp:) High rate control store table indexing Statistics (Gp:) 2 Gops Index, up to 1 Gops increment (Gp:) 4/8 (Gp:) 4/8 (Gp:) Stats per packet Byte & packet counts Traffic management Intrusion counts (Gp:) Fire & Forget R-M-W Reduces complexity (Gp:) Reduces System Latency (Gp:) C/A (Gp:) FA (Gp:) FS (Gp:) Command Addr (Gp:) 4/8 (Gp:) Frame Store (Gp:) 4/8 (Gp:) Frame Access (Gp:) Balanced read/write Frame/packet storage (Gp:) 144 Gbps (Gp:) 150M Packets/sec (Gp:) …to Backplane Other Placeholder: 28 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

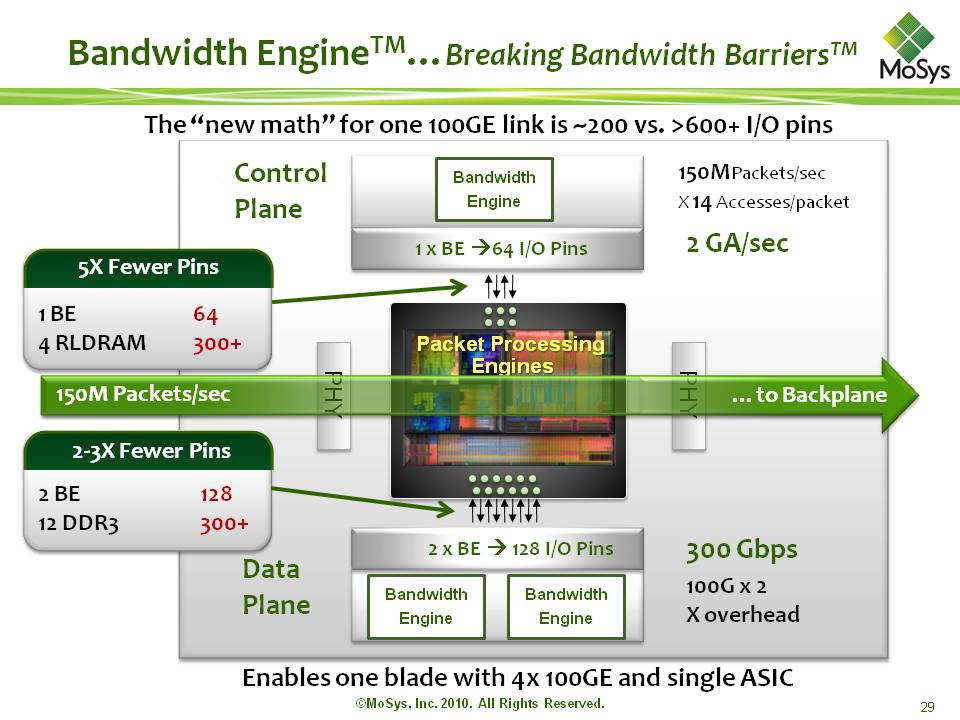

Bandwidth EngineTM…Breaking Bandwidth BarriersTM The “new math” for one 100GE link is ~200 vs. >600+ I/O pins Packet Processing Engines PHY PHY Control Plane 150MPackets/sec X 14 Accesses/packet 2 GA/sec Data Plane 100G x 2 X overhead 300 Gbps (Gp:) 2 x BE ? 128 I/O Pins (Gp:) Bandwidth Engine (Gp:) Bandwidth Engine (Gp:) Bandwidth Engine (Gp:) 1 x BE ?64 I/O Pins Enables one blade with 4x 100GE and single ASIC (Gp:) 1 BE 64 4 RLDRAM 300+ (Gp:) 5X Fewer Pins (Gp:) 2 BE 128 12 DDR3 300+ (Gp:) 2-3X Fewer Pins (Gp:) 150M Packets/sec (Gp:) …to Backplane Other Placeholder: 29 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

GigaChip™ Interface Enabling Efficient Serial Chip-to-Chip Communications

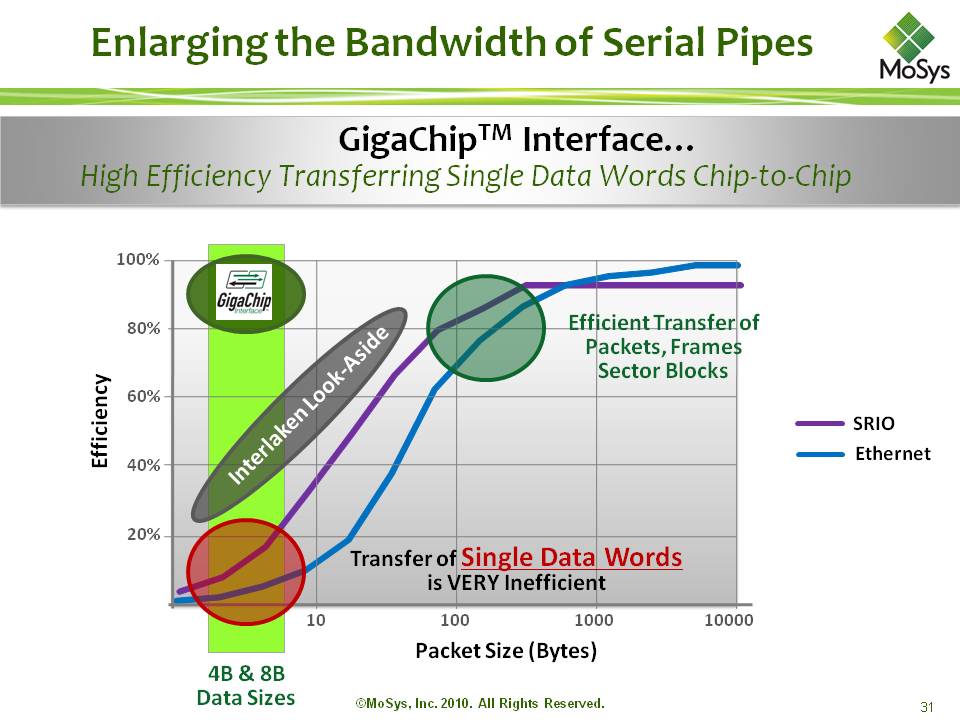

Enlarging the Bandwidth of Serial Pipes 20% 40% 60% 80% 100% Ethernet SRIO 10 100 1000 10000 Efficiency Packet Size (Bytes) 4B & 8B Data Sizes Transfer of Single Data Words is VERY Inefficient Efficient Transfer of Packets, Frames Sector Blocks Interlaken Look-Aside GigaChipTM Interface… High Efficiency Transferring Single Data Words Chip-to-Chip Other Placeholder: 31 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

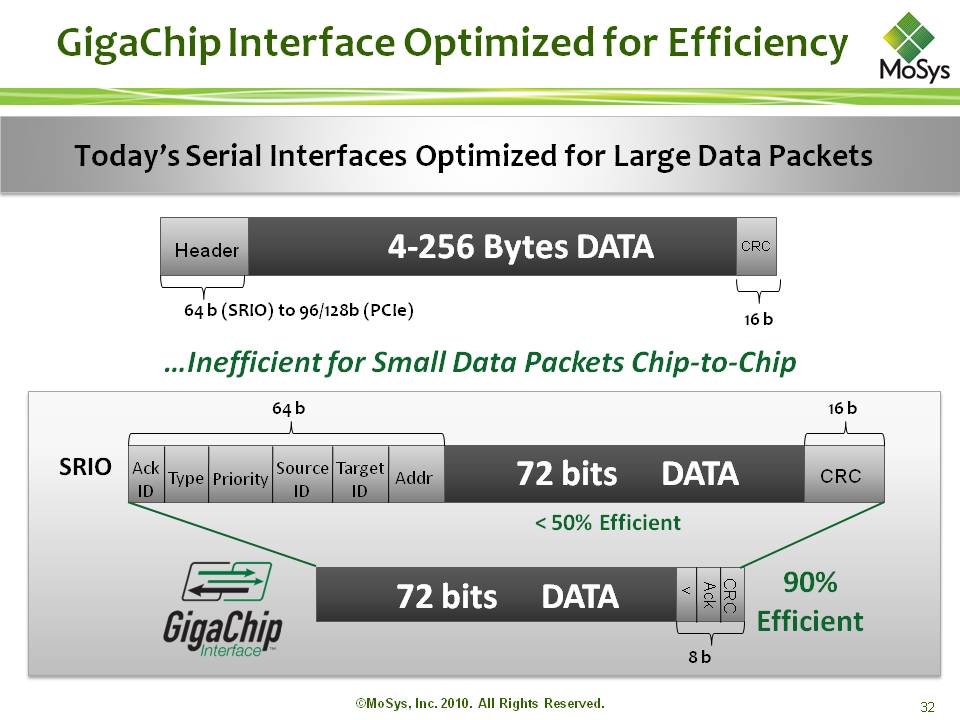

GigaChip Interface Optimized for Efficiency Other Placeholder: 32 (Gp:) SRIO (Gp:) 72 bits DATA (Gp:) Ack ID (Gp:) CRC (Gp:) < 50% Efficient (Gp:) 16 b (Gp:) 64 b (Gp:) Type (Gp:) Priority (Gp:) Source ID (Gp:) Target ID (Gp:) Addr (Gp:) 8 b (Gp:) 72 bits DATA (Gp:) CRC (Gp:) Ack (Gp:) v (Gp:) 90% Efficient 4-256 Bytes DATA CRC 16 b Header 64 b (SRIO) to 96/128b (PCIe) …Inefficient for Small Data Packets Chip-to-Chip Today’s Serial Interfaces Optimized for Large Data Packets 32 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

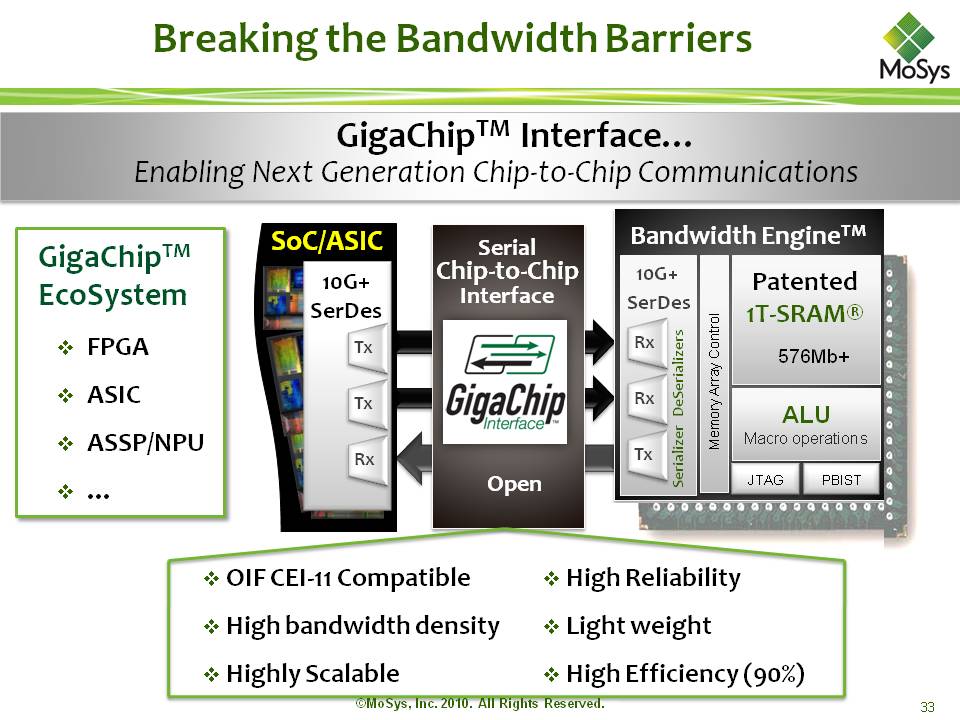

Breaking the Bandwidth Barriers Patented 1T-SRAM® Memory Array Control 576Mb+ JTAG 10G+ SerDes DeSerializers Serializer Rx Rx Tx SoC/ASIC Serial Chip-to-Chip Interface Open Tx Tx Rx 10G+ SerDes Bandwidth EngineTM PBIST ALU Macro operations (Gp:) OIF CEI-11 Compatible High bandwidth density Highly Scalable (Gp:) High Reliability Light weight High Efficiency (90%) (Gp:) GigaChipTM EcoSystem FPGA ASIC ASSP/NPU … Other Placeholder: 33 GigaChipTM Interface… Enabling Next Generation Chip-to-Chip Communications Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

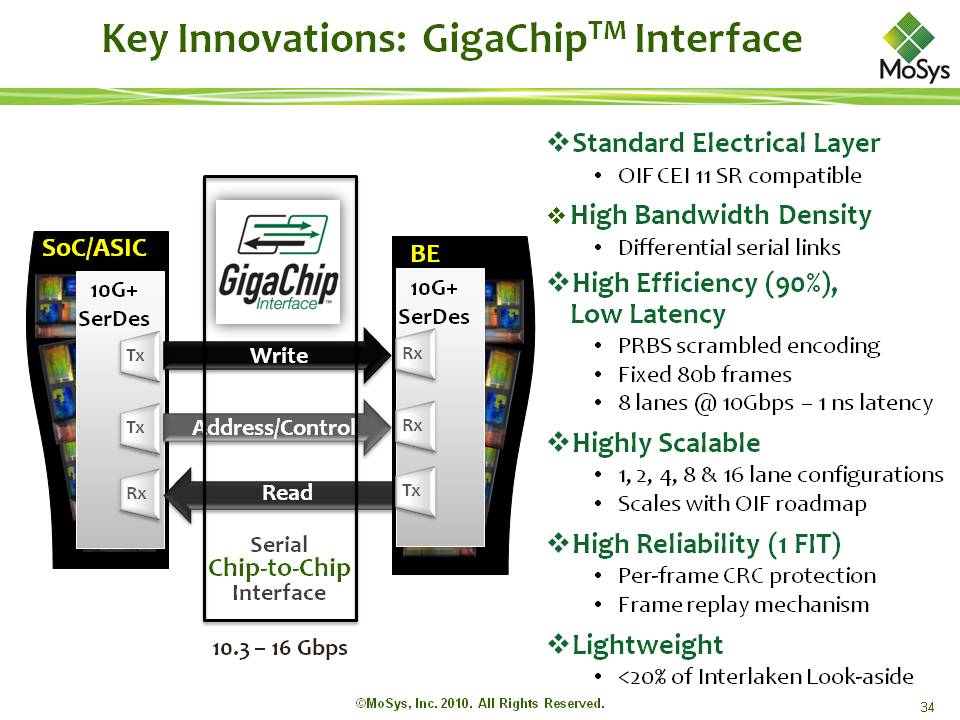

Key Innovations: GigaChipTM Interface SoC/ASIC Tx Tx Rx 10G+ SerDes Serial Chip-to-Chip Interface Write Address/Control Read BE (Gp:) Rx (Gp:) Rx (Gp:) Tx (Gp:) 10G+ SerDes 10.3 – 16 Gbps Standard Electrical Layer OIF CEI 11 SR compatible High Bandwidth Density Differential serial links High Efficiency (90%), Low Latency PRBS scrambled encoding Fixed 80b frames 8 lanes @ 10Gbps – 1 ns latency Highly Scalable 1, 2, 4, 8 & 16 lane configurations Scales with OIF roadmap High Reliability (1 FIT) Per-frame CRC protection Frame replay mechanism Lightweight <20% of Interlaken Look-aside Other Placeholder: 34 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

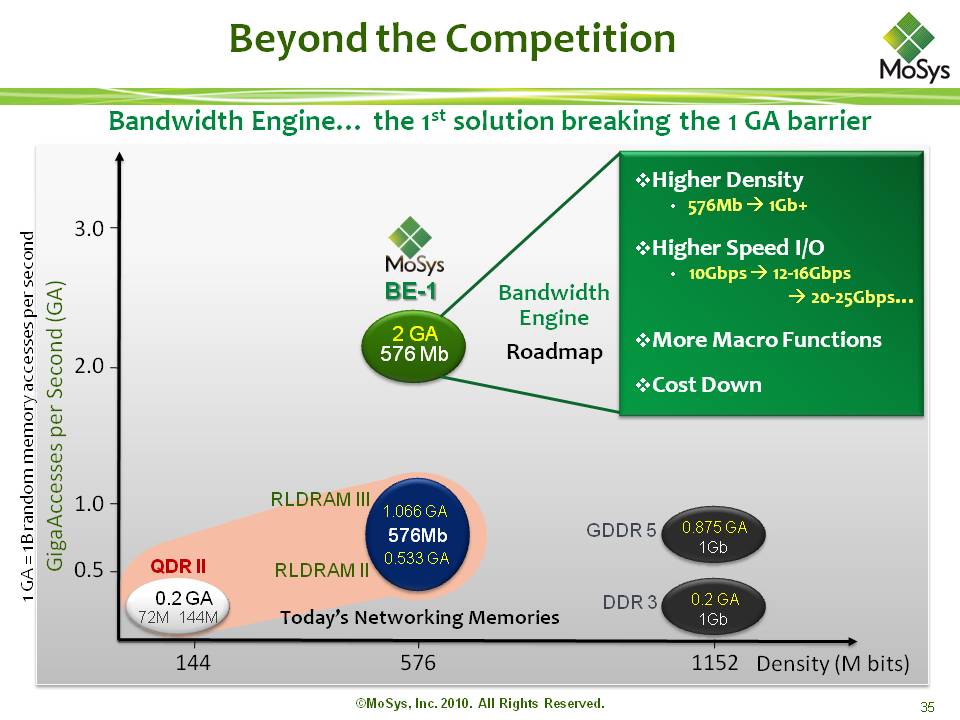

Beyond the Competition 2 GA 576 Mb 1 GA = 1B random memory accesses per second 0.5 1.0 2.0 3.0 144 576 1152 QDR II 72M 144M 0.2 GA RLDRAM III 1.066 GA 0.533 GA 576Mb RLDRAM II 0.875 GA 1Gb GDDR 5 0.2 GA 1Gb DDR 3 BE-1 GigaAccesses per Second (GA) Density (M bits) Bandwidth Engine… the 1st solution breaking the 1 GA barrier Today’s Networking Memories Bandwidth Engine Roadmap Other Placeholder: 35 (Gp:) Higher Density 576Mb ? 1Gb+ Higher Speed I/O 10Gbps ? 12-16Gbps ? 20-25Gbps… More Macro Functions Cost Down Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

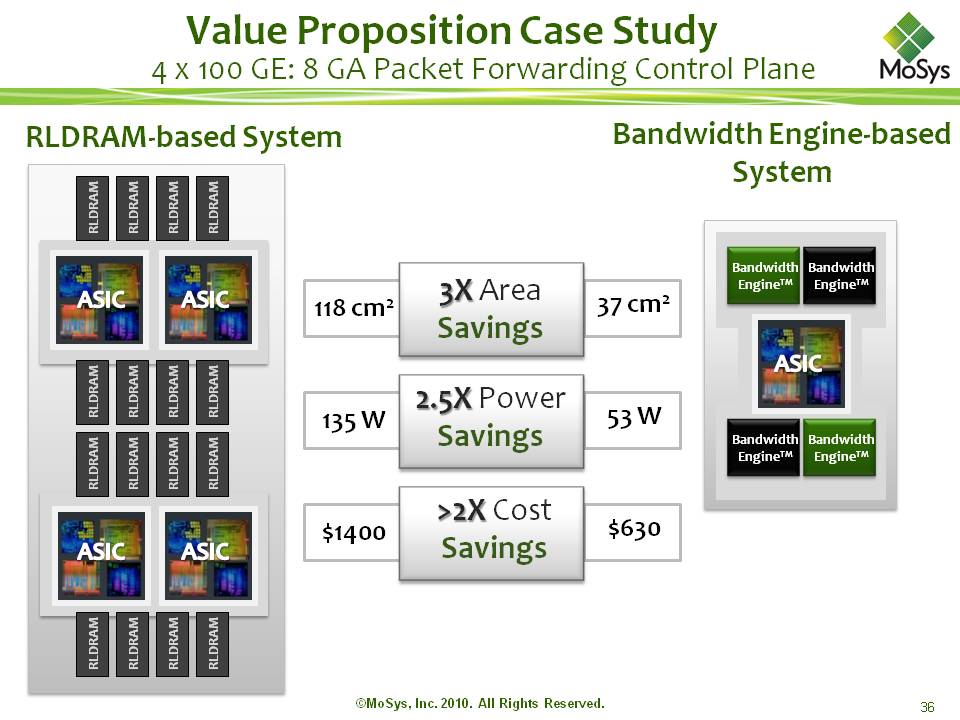

135 W $1400 $630 53 W 37 cm2 118 cm2 Title: Value Proposition Case Study 4 x 100 GE: 8 GA Packet Forwarding Control Plane (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) RLDRAM (Gp:) ASIC (Gp:) ASIC (Gp:) ASIC (Gp:) ASIC (Gp:) ASIC (Gp:) Bandwidth EngineTM (Gp:) Bandwidth EngineTM (Gp:) Bandwidth EngineTM (Gp:) Bandwidth EngineTM RLDRAM-based System Bandwidth Engine-based System 3X Area Savings 2.5X Power Savings >2X Cost Savings Other Placeholder: 36 Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

Patented 1T-SRAM® Memory Array Control 576Mb+ JTAG 10G+ SerDes DeSerializers Serializer Rx Rx Tx SoC/ASIC Serial Chip-to-Chip Interface Open Tx Tx Rx 10G+ SerDes Bandwidth EngineTM PBIST ALU Macro operations Title: Bandwidth EngineTM Solution Unparalleled Performance: 2 GigaAccesses/sec…Up to 50% lower system cost, 40% lower power Other Placeholder: 37 GigaChipTM Interface CEI-11 compatible OPEN 10G SerDes Macro Operations Read-Modify-Write More to follow 1T-SRAM ® Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.

Summary MoSys is Announcing… Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved. Expanding MoSys Business Model from ‘IP licensing’ to ‘Fabless Semiconductor and IP’ Bandwidth EngineTM – Revolutionary Family of Serial ICs that Enable Breakthrough Performance in Networking Systems GigaChipTM Interface - Open Serial Interface to Enable EFFICIENT, High Speed Chip-to-Chip Communications

Q & A Panel Other Placeholder: ©MoSys, Inc. 2010. All Rights Reserved.